sc_clock

sc_clockはモジュールにクロック信号を与えるためのシグナル。

sc_clockはsc_signalを継承しているので、基本的な扱いはsc_signalと同じ。

ただし、コンストラクタで周期とかデューティ比とかスタート時間とかを設定するようになる。

sc_clockはsc_signalを継承しているので、基本的な扱いはsc_signalと同じ。

ただし、コンストラクタで周期とかデューティ比とかスタート時間とかを設定するようになる。

クロック信号記述

sc_clock( "信号名",

周期,[単位,]

デューディ比 (初期値=0.5),

スタート時間 (初期値=SC_ZERO_TIME),[単位,]

スタートエッジ (初期値=true) );

設定例

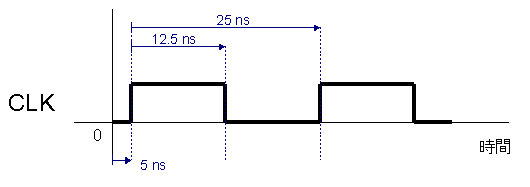

- 信号名CLK、クロック周期25[ns]、デューティ比0.5、立ち上がりエッジ5[ns]スタート

sc_clock CLK( "CLK", 25, SC_NS, 0.5, 5, SC_NS, true );

デューティ比、立ち上がりエッジ設定は省略可能。

- 信号名CLK、クロック周期10[ns] (デューティ比、エッジ省略)

sc_clock CLK( "CLK", 10, SC_NS );

- 信号名CLK、クロック周期20[us]、デューティ比0.6 (エッジ省略)

sc_clock CLK( "CLK", 20, SC_US, 0.6 );

クロック入力記述

sc_in_clk CLK; sc_in<bool> CLK;

sc_in_clkはsc_in<bool>のtypedefなので、どちらでも使えます。でも、クロックの入力としてわかりやすくするならばsc_in_clkを使ったほうがよいと思います。

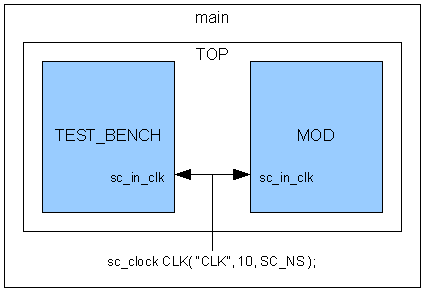

クロックの位置

sc_clockによりクロック信号を生成する場合、mainかTOPに置きます。

テストベンチにには置けません。

普通は、mainで生成します。

もし、テストベンチでクロック信号を生成したい場合は、Verilog-HDL記述のような記述が必要になります。

テストベンチにには置けません。

普通は、mainで生成します。

もし、テストベンチでクロック信号を生成したい場合は、Verilog-HDL記述のような記述が必要になります。

- main

int sc_main( int argc, char* argv[] )

{

sc_clock CLK( "CLK", 10, SC_NS, 0.5, 5, SC_NS, true );

TOP uTOP( "uTOP" );

uTOP.CLK( CLK );

・・・

sc_start();

return 0;

}

- TOP

SC_MODULE( TOP )

{

sc_in_clk CLK;

・・・

TEST_BENCH *uTEST_BENCH;

MOD *uMOD;

SC_CTOR( TOP )

{

uTEST_BENCH = new TEST_BENCH( "uTEST_BENCH" );

uTEST_BENCH->CLK( CLK );

・・・

uMOD = new MOD( "uMOD" );

uMOD->CLK( CLK );

・・・

}

};

- MOD

SC_MODULE( MOD )

{

sc_in_clk CLK;

・・・

};

- TEST_BENCH

SC_MODULE( TEST_BENCH )

{

sc_in_clk CLK;

・・・

};

テストベンチからクロックを供給する方法

クロック信号であるsc_clockはsc_signalを継承している。このため、sc_clockはプリミティブ・チャネルであるといえる。

そのため、通常はテストベンチからクロックを供給するのではなく、モデルとテストベンチを接続するトップモジュールから供給する。

荒技としてsc_exportを使用したテストベンチからのクロック供給する方法を紹介する。

そのため、通常はテストベンチからクロックを供給するのではなく、モデルとテストベンチを接続するトップモジュールから供給する。

荒技としてsc_exportを使用したテストベンチからのクロック供給する方法を紹介する。

-TestBench.h

SC_MODULE( TestBench )

{

sc_export<sc_signal_in_if<bool> > clk_p;

sc_clock clk;

SC_CTOR( TestBench )

: clk( "clk", 10.0, SC_NS )

{

clk_p( clk );

}

};

これで、clk_pポートはTestBenchのトップモジュールからみると、clk_pはsc_out<bool>と同じようにみえる。

余計な処理が増えるので、遅くなるし、わかりにくいのであまりやらない。

余計な処理が増えるので、遅くなるし、わかりにくいのであまりやらない。